티스토리 뷰

지난 포스팅에 이어서 현대반도체 Issue에 대해서 다루겠습니다.

이번 주제는 Short Channel Effect입니다.

채널을 짧게하기위해 Scaling을 하는데 이는 회로의 전체적인 크기를 70%의 크기로 축소하는 것입니다.

왜 하필 70%를 축소하는 것일까요?

예를들어 길이가 1인 정육면체를 생각해보겠습니다.

위 정육면체의 가로 세로를 전부 70%만큼 축소시켰습니다.

이때의 면적의 차이는 기존 1x1=1에서 0.7x0.7=0.49로 줄었습니다.

즉, 면적을 절반으로 만들기 위하여 전체 크기를 70%로 줄이는 것입니다.

그리고 소자가 작아진 만큼 내부의 Electric Field의 값을 다소 일정하게 유지하기 위해 값을 줄여야만합니다.

이러한 전체적인 과정이 Scaling이라고 합니다.

이제 Scaling을 통해 나타나는 반도체소자의 Issue에 대해서 살펴보겠습니다.

[ Short Channel Effect - Scaling Issue ]

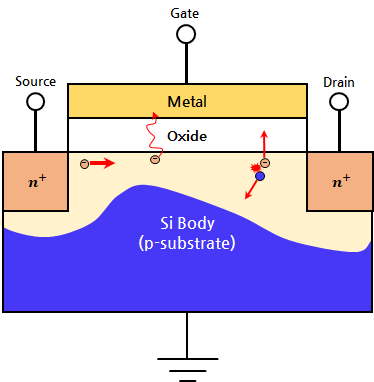

위 그림은 Scaling으로 인해 나타나는 Issue들을 그림으로 표현해본 것입니다.

이제 각각의 Short Channel Effect Issue들을 자세하게 설명드리겠습니다.

① Subthreshold Current

소자를 전체적으로 Scaling하면 문턱전압 등 다른 소자값들도 그에맞게 Scaling됩니다.

그러다보니 현재 Threshold Voltage값은 0.7V이하의 값으로 내려오게되었습니다.

이때 발생할 수 있는 문제점은 문턱전압의 값이 작기 때문에,

그만큼 문턱전압이하에서 누설전류가 발생할 확률이 높아집니다.

이러한 과정은 지난 포스팅에서 자세히 다루었기 때문에 해당 글 참고하시기 바랍니다.

2019/11/19 - [전자공학/반도체] - 24강. MOSFET Subthreshold Current

② Hot Carrier Effect / Impact Ionization

채널의 길이가 짧아진 만큼, 전자는 전기장에의해 쉽게 가속되어 속도가 빨라집니다.

그리고 전자가 채널을 이동하면서 Space Charge들과 Scattering 즉, 충돌을 하며 이동합니다.

이러한 과정에서 전자가 열을 발생시켜 Hot Carrier라고 부릅니다.

단지 소자에 열을 발생시킬 뿐만아니라, 큰 속도로 가속된 전자가 주변의 원자들과 큰속도로 부딪히게되면

그 충돌에 의해 원자가 이온화되어 EHP(Electron Hole Pair)를 발생시키게 됩니다.

그리고 이 이온화된 전자와 정공은 전계에 의해 전자는 Gate나 Drain으로 정공은 Body쪽으로 이동하게됩니다.

이 전자와 정공들의 농도가 높아지게되면 소자의 신뢰성을 떨어뜨려 올바르게 동작하지 못합니다.

③ Substrate Current

②과정에 의해 발생한 정공이 Body쪽으로 이끌려가면서 생기는 전류성분입니다.

일종의 Diffusion Current와 같은 종류의 전류성분으로, 의도하지 않은 누설전류라 할 수 있습니다.

④ Tunneling

Scaling에 의해 Gate의 두께 역시 얇아지게되는데, 이때 전자들이 채널을 통해 드레인으로 이동하는 도중에

Gate영역으로 Tunneling되어 의도하지 않은 누설전류를 발생시킵니다.

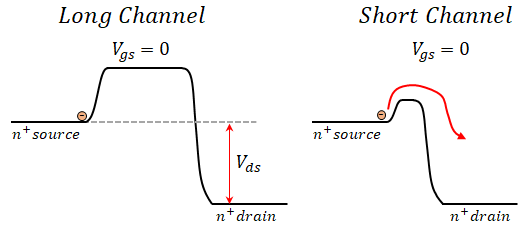

⑤ DIBL ( Drain Induced Barrow Lowering) , 드레인 유기 장벽 감소

채널의 길이가 짧아진 MOSFET을 살펴보겠습니다.

대비를 위해 Long Channel과 Short Channel MOSFET의 에너지 밴드다이어그램을 확인하겠습니다.

먼저 Long Channel에서는 Drain전압에의해 채널의 장벽이 낮아지지 않기때문에, 전자가 넘어갈 수 없습니다.

하지만 Short Channel에서는 채널의 길이가 짧아진 만큼, Drain전압에 영향을 받기가 쉽습니다.

따라서 장벽의 에너지가 Vgs가 인가되지 않더라도 Vds만에 의해서 장벽이 낮아집니다.

이러한 이유로 트랜지스터가 ON되지 않아도 전자가 Drain으로 넘어가게 되는 것입니다.

⑥ GIDL (Gate Induced Drain Leakeage) , 게이트 유기 드레인 누설

일반적으로 Vgs<0으로 유지되면, Off Current가 거의 없는 상태가 됩니다.

하지만 큰 음의방향의 Gate전압이 인가하거나 양의방향의 Gate전압이 인가된다면

Gate와 Drain사이의 채널에 캐리어들이 축적됩니다.

이러한 캐리어들이 Band를 더 휘어지게 만들게되고, Tunneling을 통해 EHP를 발생시켜 누설전류를 발생시킵니다.

이러한 누설은 Drain과 Substrate간에 누설전류의 성분이 됩니다.

⑦ Punch Through 현상

채널이 짧아지면서 Source와 Drain사이의 거리 또한 가까워 집니다.

이때 Source와 Drain영역에 형성된 공핍영역이 채널 아래부분에서 만나게 되면,

공핍영역에 존재하고 있는 전자들이 이 부분을 통해서 드레인 영역으로 이동하여 전류가 누설되게 됩니다.

Punch Through 발생 조건은 Off 상태일 때(Vgs와 무관), 약간의 Vds전압이 인가되어 발생할 수 있습니다.

'전자공학 > 반도체' 카테고리의 다른 글

| 27강. High-K Metal Gate (1) | 2019.11.22 |

|---|---|

| 26강. Strained Silicon (1) | 2019.11.21 |

| 24강. MOSFET Subthreshold Current (0) | 2019.11.19 |

| 23강. DRAM, SRAM, Flash Memory (1) | 2019.11.18 |

| 22강. MOSFET Noises (0) | 2019.11.17 |