티스토리 뷰

이번강에서는 7강에서 자세히 다루지 못했던 부분 한번 더 짚고 넘어가는 포스팅 하도록 하겠습니다.

지난번 포스팅에서 설명드렸던 Clock신호입니다.

여기서 의문이 드는점은 어떻게 구현을 해야 상승에지, 하강에지에서 입력을 받을 수 있을까요?

D플립플롭을 예로 들어 설명하겠습니다.

Master-Slave 즉, 주종 플립플롭이라고 하며 Slave측의 입력은 Master측 출력에 종속되는 구조입니다.

이제 위 회로의 타이밍도를 보면서 에지트리거가 구현되는지 확인해보겠습니다.

첫번째 D래치의 출력 Q0가 두번째 D래치의 입력으로 들어가게되고, 두번째 D래치는 Low Level Trigger입니다.

따라서 Q의 타이밍도는 Clock신호가 low level상태일때 Q0의 입력에 영향을 받게되어 출력됩니다.

즉, 위의 Master - Slave형 D플립플롭은 하강에지트리거로 동작하게 되는 것입니다.

지금까지 제가 포스팅했던 타이밍도를 보면 입력에 따라 출력이 즉각적으로 나옴을 확인했습니다.

하지만 실제로는 입력이 들어가면 바로 출력이 나오는것이아니라, 어느정도의 시간지연이 생깁니다.

실제로는 상승에지에서 D라는 입력이 들어와도 바로 출력으로 나오지 못하고, 어느정도의 시간지연을 가지고 출력으로 나옵니다. 현재는 D플립플롭 하나를 이용하기때문에 큰 문제없이 시간지연만 나오는 형태로 보입니다.

하지만 복잡한 시스템에서는 여러개의 플립플롭, 조합논리회로들, clock들끼리도 신호차이가 발생하기때문에 delay문제가 가장 큰 문제로 자리잡게됩니다.

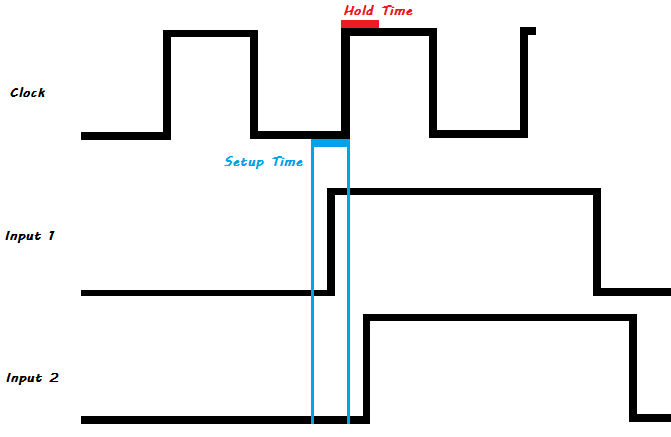

※ Setup Time과 Hold Time

① Setup Time

상승(하강)에지 전, 입력으로 받아들이는데 필요한 최소시간.

이 Setup Time을 만족하지 못할 때, 입력신호가 정상적으로 소자에 입력되지 못합니다.

이러한 현상을 Setup Time Violation 이라고 합니다.

위 타이밍도에서 Input 1을 먼저 보겠습니다. Setup Time을 만족하지 못하는 케이스입니다.

상승에지 이전에 Setup Time동안 입력으로 들어오는 신호가 0에서 1로 바뀌고 있습니다.

이럴 경우에 입력신호는 0인지 1인지 판별할 수 없는 문제가 발생합니다.

하지만 Input 2의 경우는 Setup Time동안 신호가 바뀌지않고 유지됩니다. 이때는 입력이 0으로 정상적으로 입력됩니다.

② Hold Time

상승(하강)에지 후, 출력으로 유지하기위해 필요한 최소시간.

Hold Time도 만족하지 못하는 경우, 출력신호가 유지되지못하고 원하는값을 얻지못하게됩니다.

위 타이밍도에서 Input1은 Hold Time을 만족하지 못합니다. 상승에지 이후에 신호를 유지하지 못하고 0에서 1로 바뀌고 있습니다. 이 경우에도 정상적인 출력을 할 수 없습니다.

반면 Input2의 경우 Hold Time동안 신호가 바뀌지 않고 유지됩니다.

오늘 포스팅은 Master-Slave형 플립플롭을 통해서 에지입력을 받게되는 원리와 Setup Time, Hold Time에 대해서 진행했습니다. 부족한점있거나 틀린내용있으면 지적해주시면 바로바로 수정할 수 있도록하겠습니다.

오늘도 읽어주셔서 감사합니다 :)

'전자공학 > 논리회로' 카테고리의 다른 글

| 10강. 카운터 ( 동기 카운터, 비동기 카운터 ) (1) | 2019.06.12 |

|---|---|

| 9강. 레지스터 (0) | 2019.06.11 |

| 7강. 순서논리회로 - 래치와 플립플롭(2) (0) | 2019.06.09 |

| 2-2강. 디지털 시스템과 2진수 체계 (0) | 2019.06.01 |

| 0강. 디지털과 아날로그에 대하여 (1) | 2019.05.29 |